•

•

.

•

•

•

•

•

•

•

| 1) |  |

|----|--|

Over operating free-air temperature unless otherwise noted<sup>(1)</sup>

| DESCRIPTION                                   | MIN  | MAX | UNIT |

|-----------------------------------------------|------|-----|------|

| VIN, EN                                       | -0.3 | 32  | V    |

| SW                                            | -1   | 32  | V    |

| BST                                           | -0.3 | 38  | V    |

| BST-SW                                        | -0.3 | 6   | V    |

| VOUT                                          | -0.3 | 16  | V    |

| 5.0V, EN_LDO, MODE, VCC, FB                   | -0.3 | 6   | V    |

| Operating junction temperature <sup>(2)</sup> | -40  | 125 | С    |

| Storage temperature T <sub>STG</sub>          | -65  | 150 | С    |

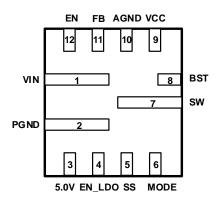

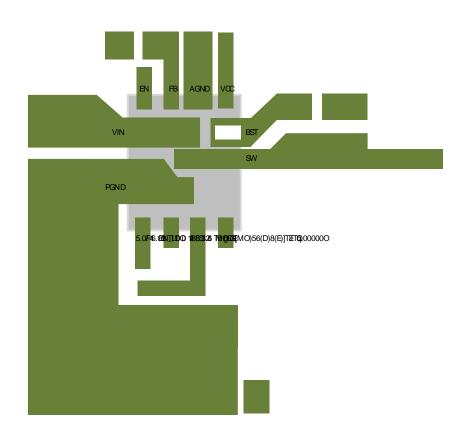

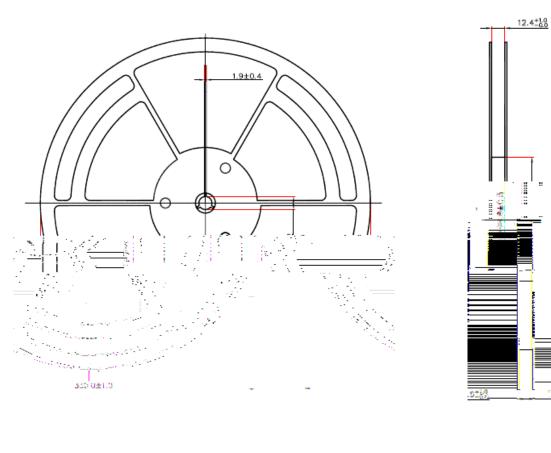

Top View: QFN-12L 3mm x 3mm, Plastic

(1)

(2)

| VIN    | 1 | Input voltage. Decouple the input rail with at least a 0.1uF and 10uF input ceramic capacitor. Place the capacitor as close to VIN and PGND pins as possible. Use wide PCB traces and multiple vias to make the connection. |

|--------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGND   | 2 | Power ground. Using wide PCB traces and multiple vias large enough to handle the load current.                                                                                                                              |

| 5.0V   | 3 | The output of the 5.0V, 150mA LDO output, at least a 4.7uF ceramic cap connected between VCC pin and ground.                                                                                                                |

| EN LDO |   |                                                                                                                                                                                                                             |

EN\_LDO 4

| SW   | 7  | Switch output. SW is driven up to VIN through the high-side power MOSFET during on-time. The inductor current drives SW to negative voltage through low-side power MOSFET during off-time. Use wide and short PCB traces to make the connection. Keep the SW pattern area minimized. |

|------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BST  | 8  | Bootstrap. Must connect a 0.1uF capacitor or greater between SW and BST to form a floating supply across the gate driver of high-side power MOSFET.                                                                                                                                  |

| VCC  | 9  | Internal VCC LDO output. The driver and control circuits are powered by VCC. Decouple with 1µF ceramic capacitor placed as close to VCC as possible.                                                                                                                                 |

| AGND | 10 |                                                                                                                                                                                                                                                                                      |

|   |  |   |   | <u> </u> |  |

|---|--|---|---|----------|--|

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  | I |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   | T |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   | <u> </u> |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

| - |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

| _ |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   | • |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  |   |   |          |  |

|   |  | - | • | •        |  |

| <u> </u> |               |  |

|----------|---------------|--|

|          |               |  |

|          |               |  |

|          | <del></del> ' |  |

| _        |               |  |

| •        |               |  |

|          |               |  |

|          |               |  |

|          |               |  |

|          |               |  |

|          |               |  |

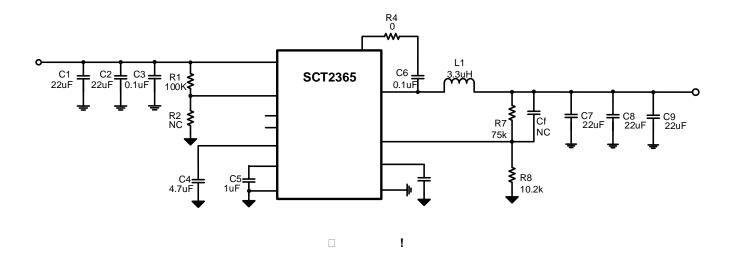

| Design Parameters                    | Example Value |

|--------------------------------------|---------------|

| Input Voltage                        | 12V           |

| Output Voltage                       | 5V            |

| Output Current                       | 6A            |

| Output voltage ripple (peak to peak) | 50mV          |

| Switching Frequency                  | 400kHz        |

\*

•

\_\_\_\_

2.

3.

4.

5.

6.

|  | _ |  |

|--|---|--|

|  | _ |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

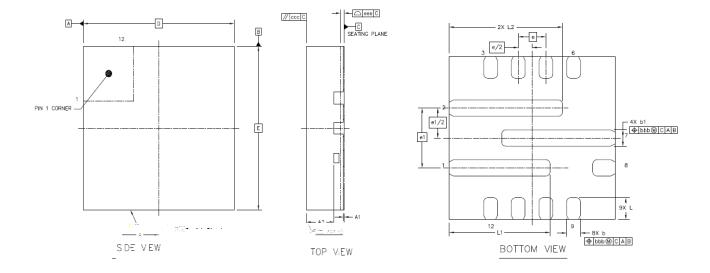

1. 2. 3. 4. 5.

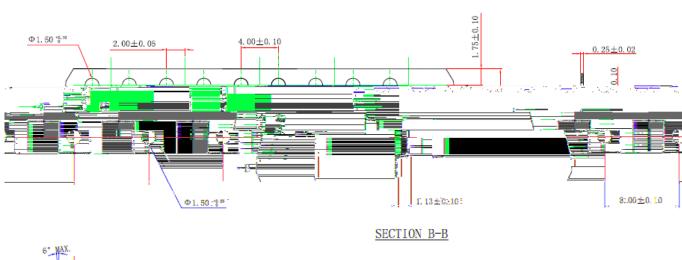

SECTION A-A